■内置700V高雪崩能力功率MOSFET

■9Vto38V宽范围VDD电压

■内置高压启动电路,无需外部启动电阻

■电流控制模式

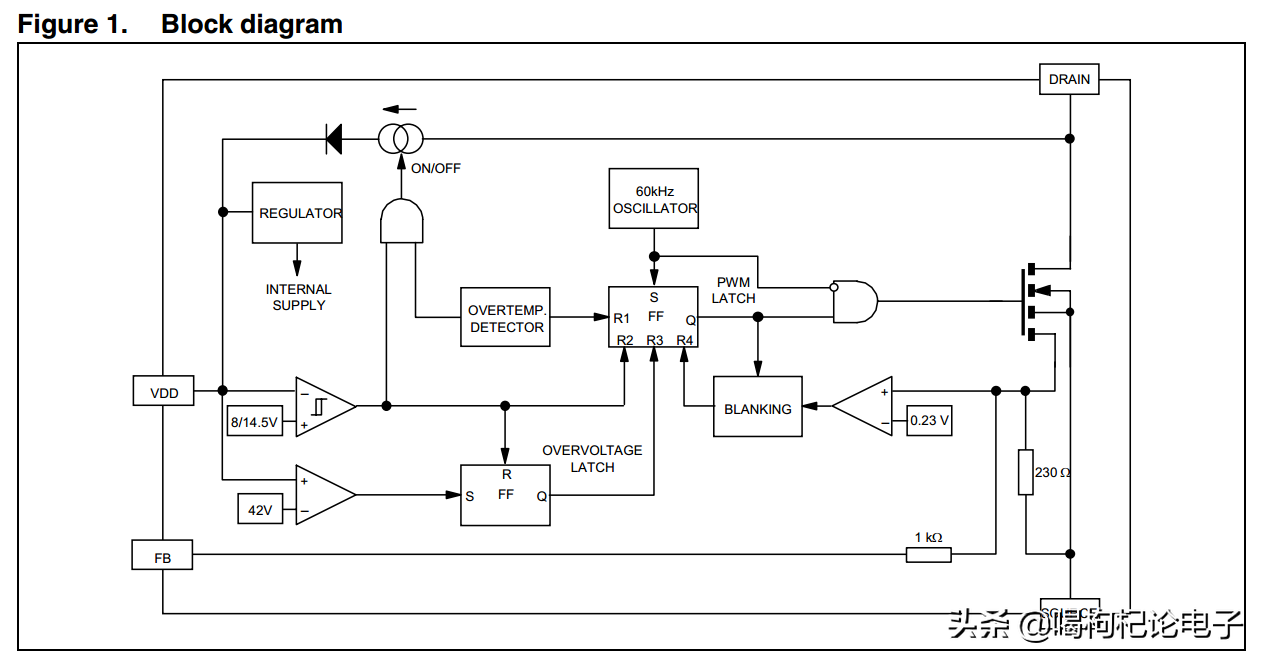

下面是芯片内部框图

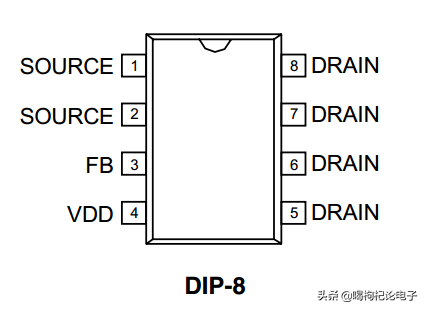

芯片管脚定义

SOURCE:接内部功率MOS源极,同时也是控制回路的参考地。

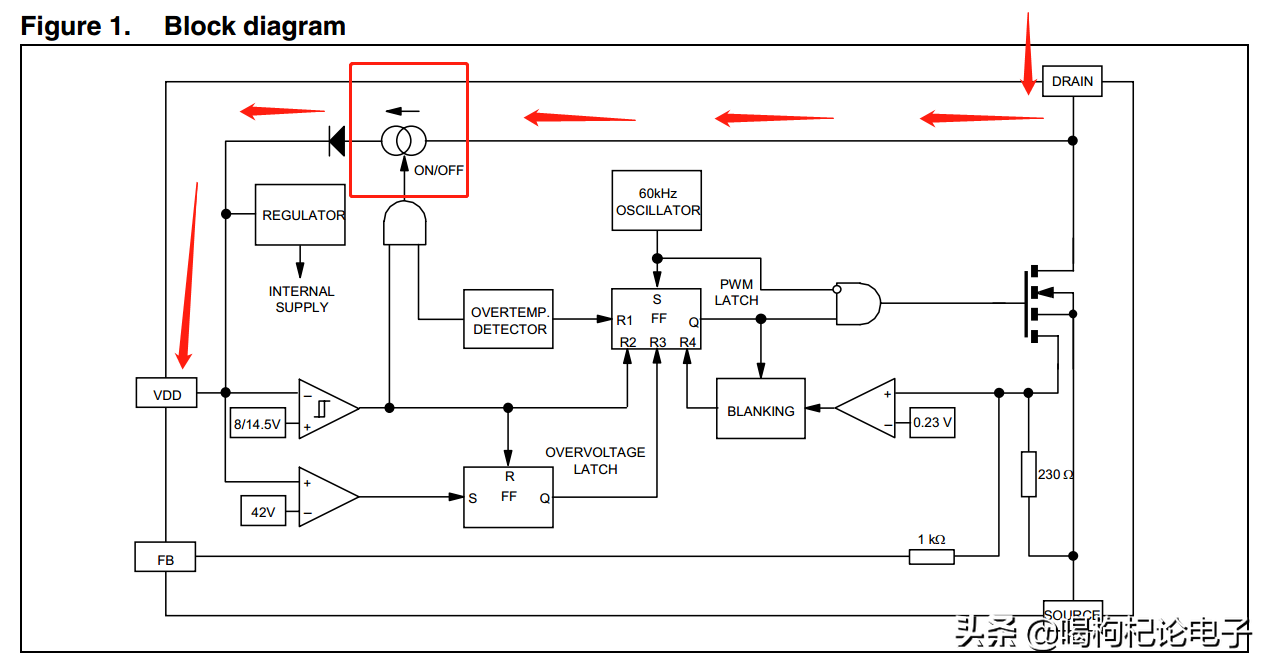

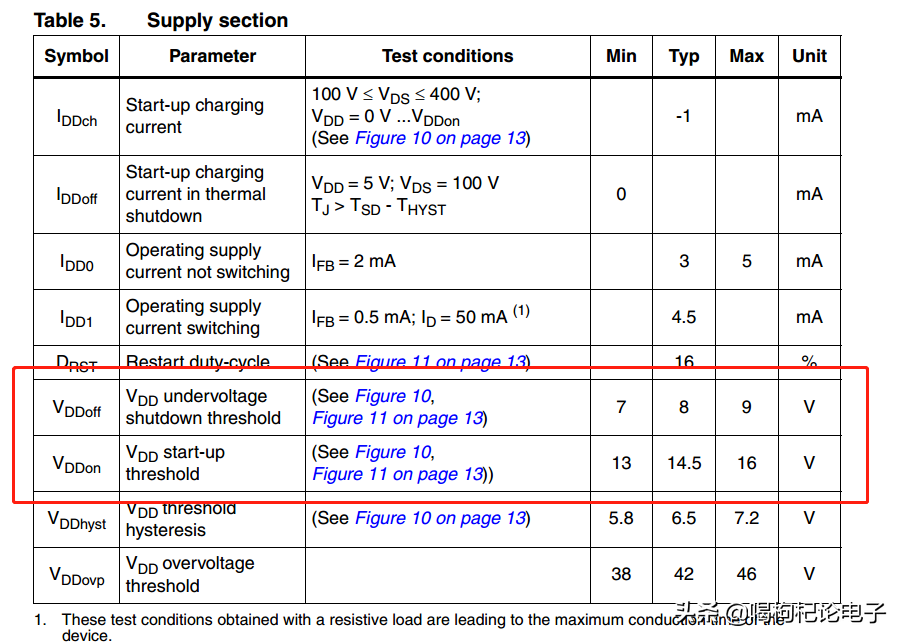

VDD:控制电路的供电电源,VIPER22A没有外部启动电阻,精简了电路。启动时漏极的高压进入芯片,然后芯片内部高压电流源开关打开,对VDD电容进行充电(下图1),当达到启动电压时,内部高压启动电路关闭。内部迟滞比较器监测VDD电压,并提供两个阈值,VDDon和VDDoff(下图2).VDDon值为14.5V,当VDD电压达到14.5V,此时高压电流源开关断开,关闭启动电流源,电源启动后VDD电容的能量将由变压器提供,VDDoff电压为8V.当VDD电压降到8V,此时高压电流源开关打开,由高压电流源对VDD电容充电。此处为何要设两个阈值?试想一下,如果只设定一个启动值VDDon的话,电源能启动吗?举例说明,当VDD电容充到14.5V时,芯片启动,内部振荡器等电路开始工作,这些模块工作是要消耗电流的,也就是说,当电源刚刚启动起来,因为内部模块的消耗,VDD电容会立即跌落到14.5V以下,芯片会停止启动,接着高压电流源继续对DD电容充电,充到14.5V时芯片又开始工作,周而复始,芯片始终处于启动--停止--启动的循环状态,一直到天荒地老,芯片将不能正常启动。这是设定VDDoff阈值的好处就体现出来了,设定了VDDoff阈值后,就会形成一个回差,差值为6.5V.由于这个差值的存在,在VDD电压跌落到8V以前,芯片已经正常启动完成了,芯片启动完成后,将由变压器辅助绕组源源不断的提供电流给VDD电容,这时电源启动完成。

图1内部高压电流源对VDD电容充电

图2

DRAIN:功率MOS的漏极。

图3

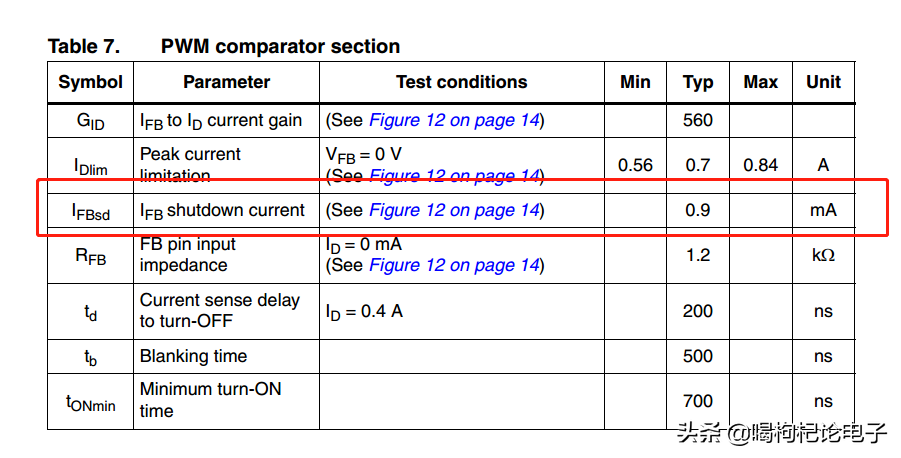

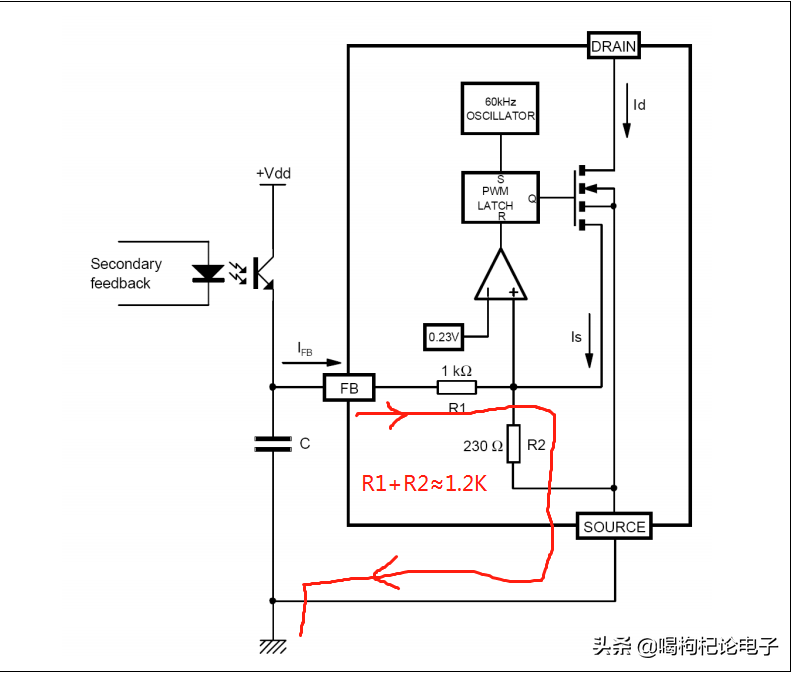

下面详细讲解FB引脚内部的功能:

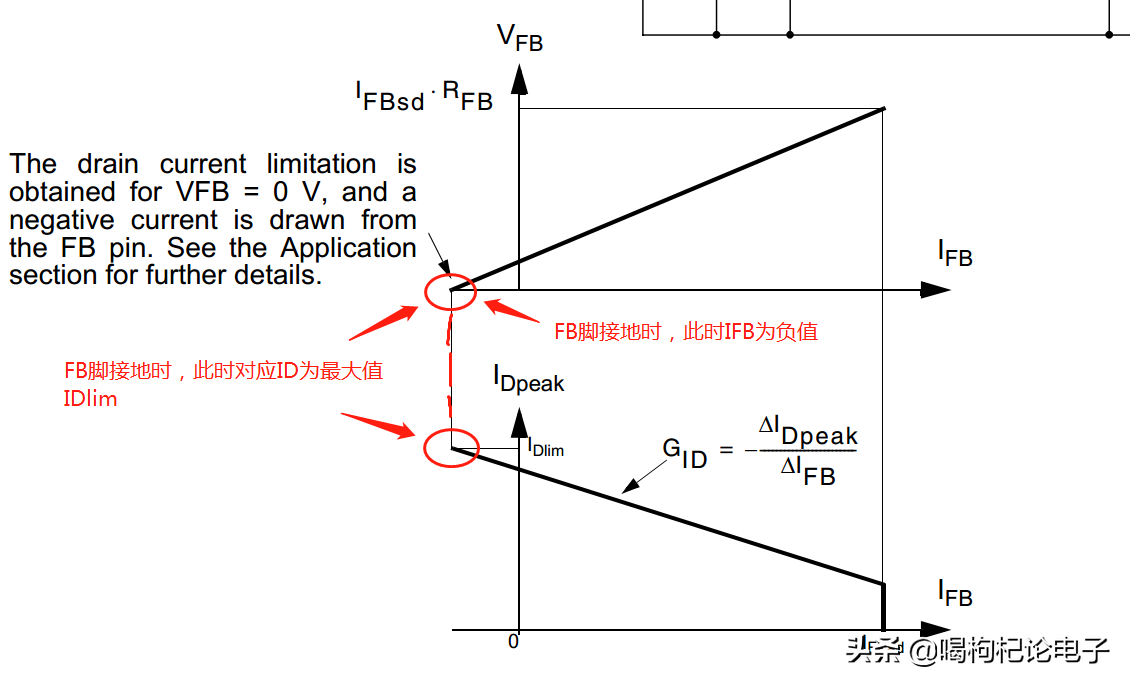

图4

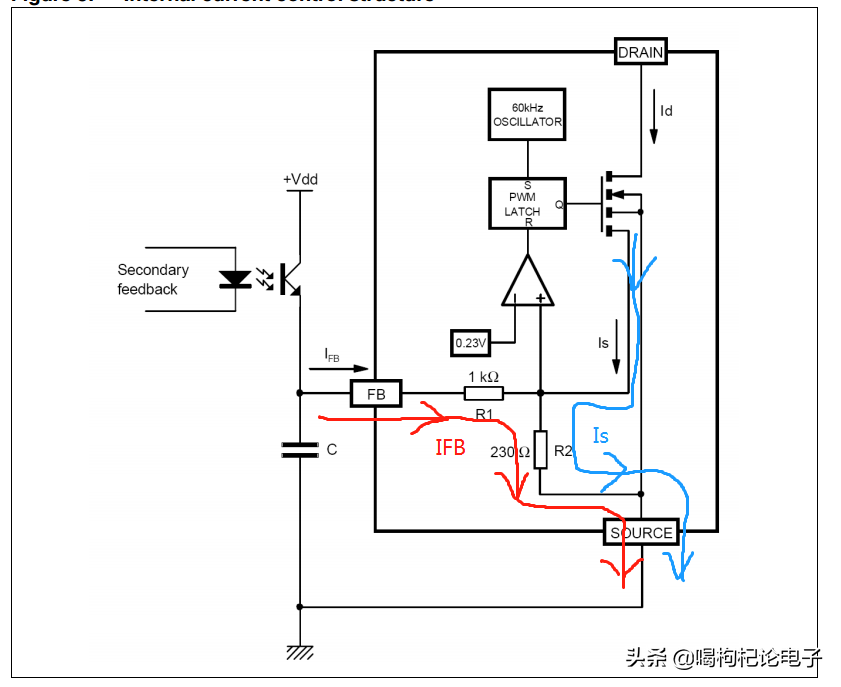

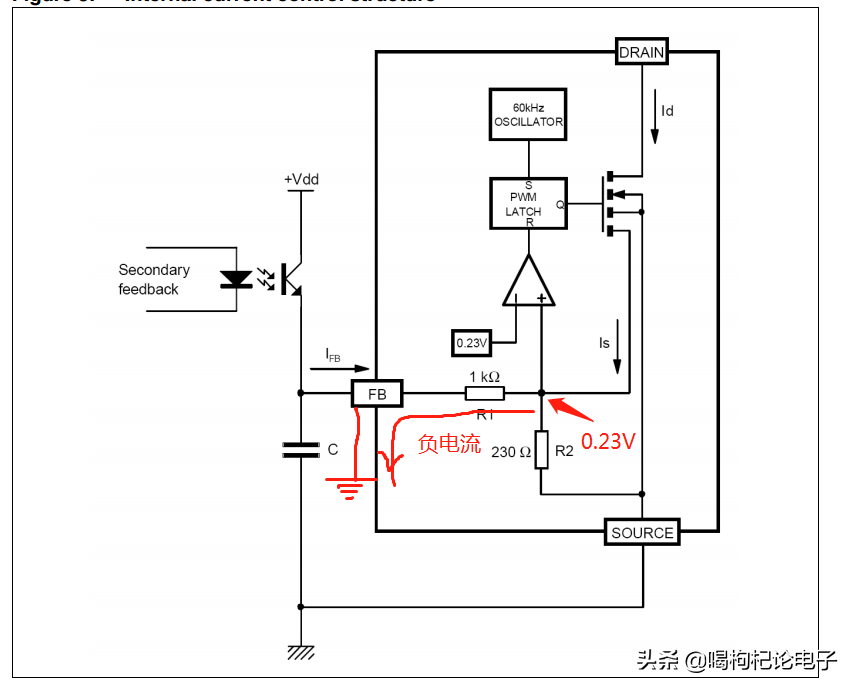

根据上式R2(Is+IFB),可以轻松的推导出Is=(0.23V/R2)-为功率MOS上Is和Id的映射比例关系函数(如图5),可得出Id=Gid*Is=Gid[(0.23V/R2)-IFB].当将FB引脚接地时将得到最大的Id值即IDlim.此时FB脚将流过1个负方向的电流(下图6),IFB=-(0.23V/R1).MOS漏极最大值IDlim=Gid*0.23V*(R1+R2)/(R1*R2)

图5

图6

在实际应用中,FB引脚往往是被1个外部光耦驱动的,光耦的C极上拉的电源,所以在这种应用场合下,FB脚并不能真正的短接到地,所以上式最大的IDlim是不可能达到的。然而,图中FB脚并联有稳定FB引脚电压的电容C,当光耦关断时(电源刚启动时或电源次级短路时),因此我们可以假定此时FB脚的电压非常接近为零。

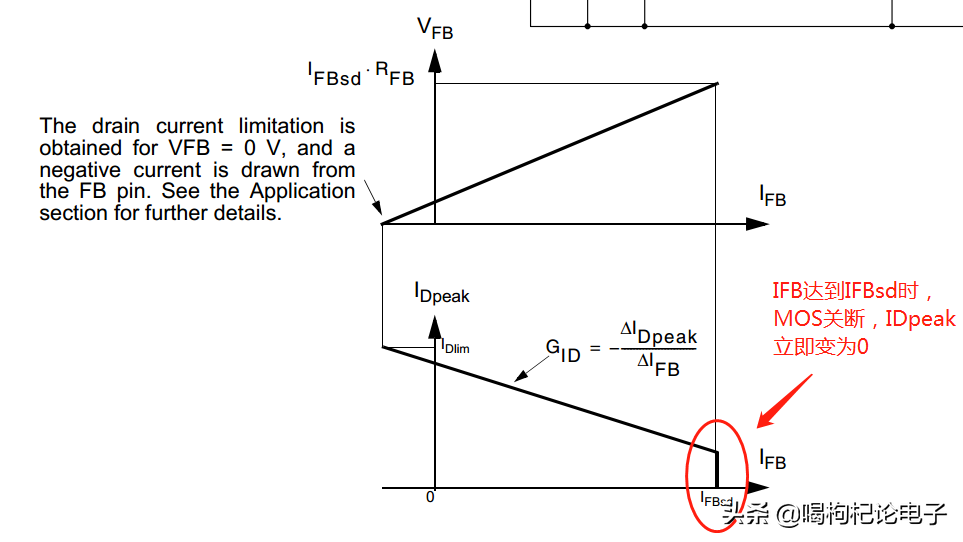

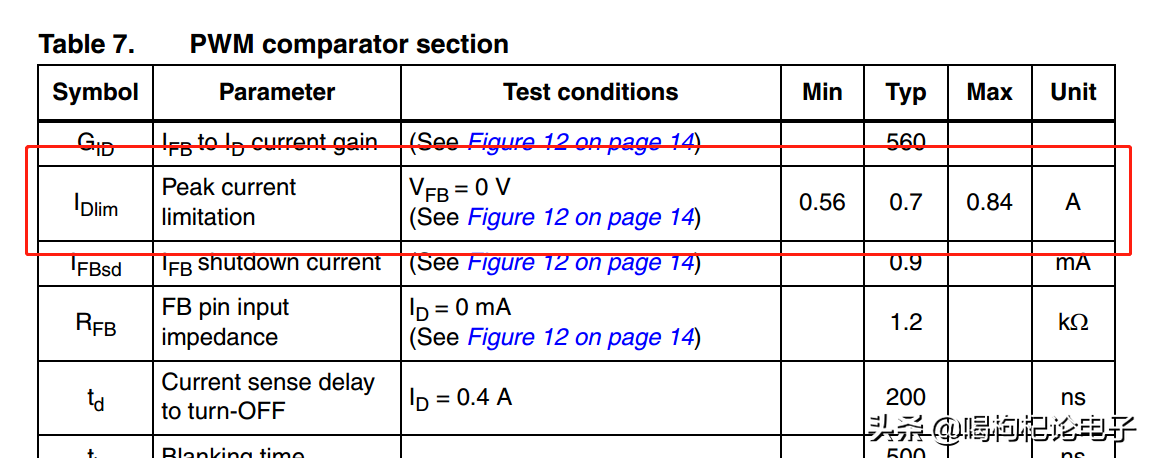

IFBsd为芯片内部设定的阈值(如上图3),正常工作时IFBIFBsd,当IFB超过这个阈值(0.9V)时,内部功率MOS会停止开关。如下图7,8

图7

图8

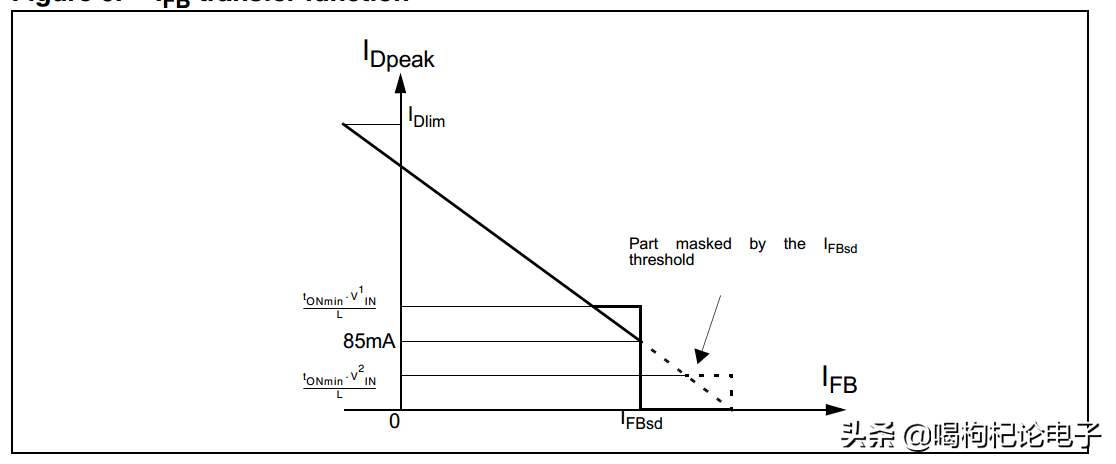

IFBsd的值由内部的PWM比较器所决定的,实际上当漏极电流ID大约等于IDlim的12%时(下图9),也就是约85mA时,芯片进入burstmode模式,改善轻载下的待机功耗。见下图10

图9

图10

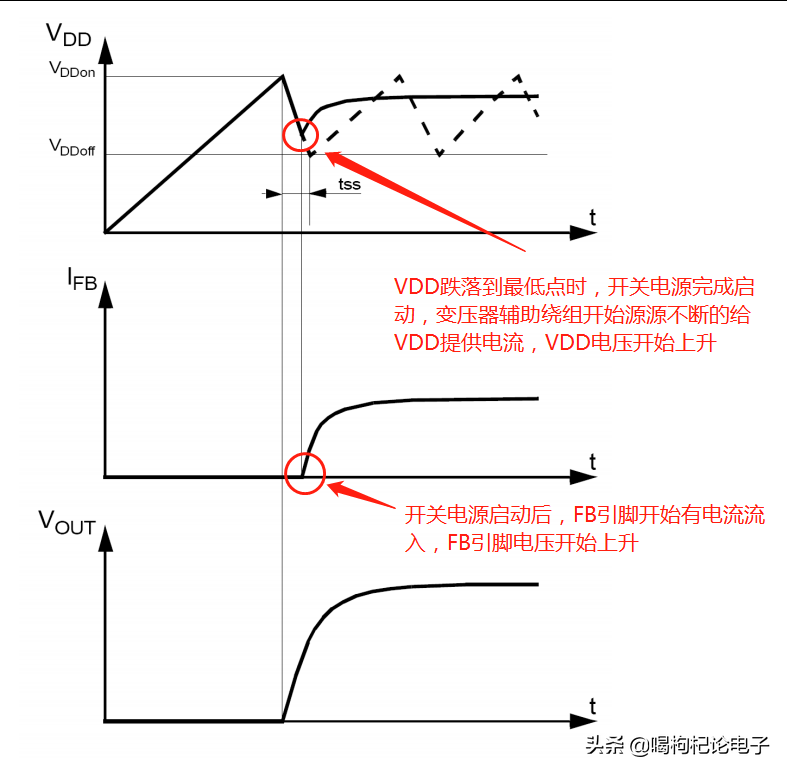

芯片启动时序芯片内部漏极上连接有高压启动电流源,当整流后的高压进入到漏极引脚,内部的高压启动电流源开始工作,对VDD电容进行充电,当电容上的电压达到VDDon时,高压启动电流源关闭,芯片内部电路开始工作,推动功率MOS产生开关动作,此时因为电源次级电压还没有建立起来,FB引脚无法从光耦得到电流,芯片将以全功率状态运行,随着次级输出电压上升,直到达到调节点,光耦初级发光二极管开始工作,FB引脚得到电流,芯片开始环路调控。调控过程如下,当次级电压升高,光耦电流加大,IFB加大,功率MOS漏极电流Id减小,变压器初级绕组储存的能量减少,次级电压下降。次级电压降低的调节过程与上面相反,此处不再累述。请看下图,图11

上图中最上面虚线部分表示的是,电源启动失败的波形,如果在VDD上的电压跌落到VDDoff以前,电源还没有启动完成,也就是说VDD上的电容上的能量因为芯片内部模块的启动一直在消耗能量,直到电压跌落到VDDoff.电源还没有启动完成,辅助绕组还未提供能量给VDD电容,电源将启动失败,虚线的波形就是VDD电容在一直充电放电的过程。

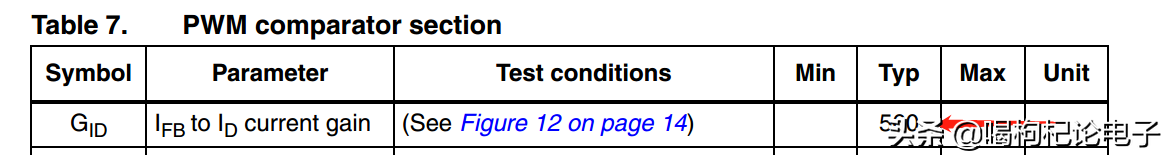

接下来再讲讲Datesheet中其它的一些参数:

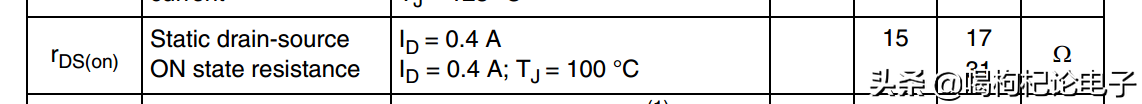

RDSon

RDSon为芯片内部功率MOS的漏源间的导通电阻,从上图可以看出,温度对RDSon有影响,温度越高,RDSon越大,这就要求我们设计时要充分考虑芯片的温升。

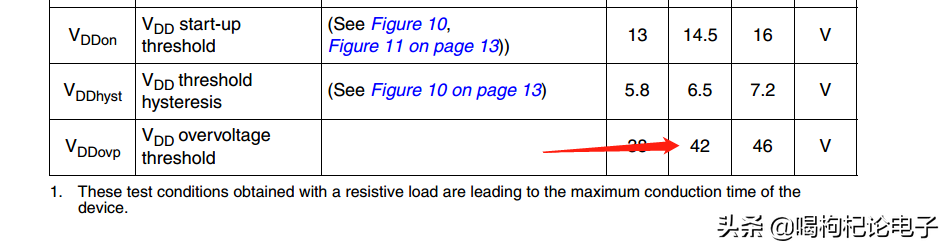

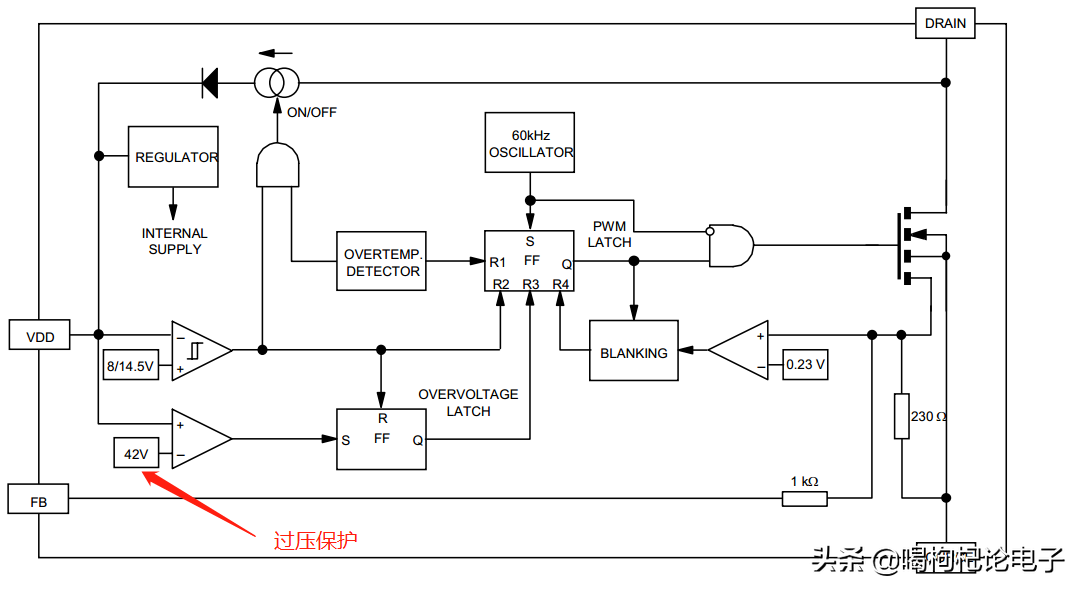

芯片内部集成有过压检测,当VDD电压超过42V,内部电路锁定,当电压恢复正常,芯片自动恢复正常工作。

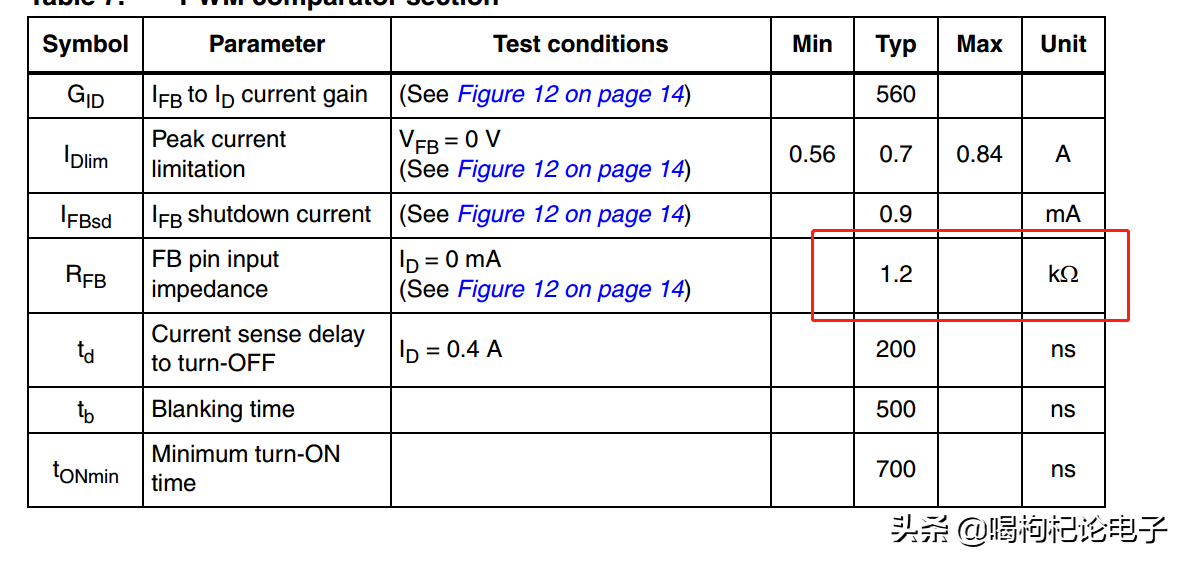

FB脚输入阻抗

FB脚输入阻抗为1.2K,怎么来的?看下图就明白了。

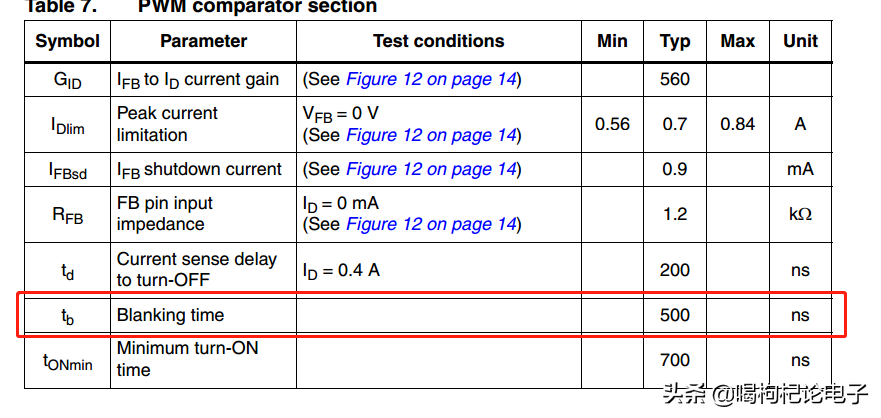

前沿消隐:由于SW脚的寄生电容,当MOS开通瞬间存在较大的峰值电流,如果采样MOSFET采样到该信号,芯片会进入过流保护状态。为了防止MOS开通瞬间引起电路误触发,过流保护电路在功率管开通一段时间(典型值500ns)后才开始工作。